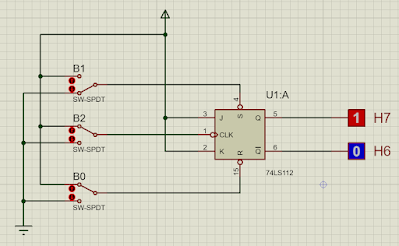

Pada percobaan 2 IC yang digunakan adalah 74LS112 dimana untuk J dan K dihubungkan bersamaan dengan VCC. B1 dihubungkan ke pin S, B0 dihubungkan ke pin R, dan B2 dihubungkan ke CLK. Untuk pin S dan R adalah aktif low, dimana akan aktif apabila berlogika 0. Pada rangkaian percobaan diatas apabila di simulasikan maka B1 = S = 0, B0 = R = 1. karena aktif low, maka flip-flop akan dalam keadaan SET, dimana output Q akan berlogika 1 dan komplemennya Q' berlogika 0. Pada percobaan, B1, B0, dan B2 divariasikan.

- Apabila B1= 1, B0 = 0, B2 = Don't Care sedangkan pin S dan R aktif low, maka flip-flop dalam keadaan Reset. Sehingga output akan berlogika 0 dan komplemennya berlogika 1.

- Apabila B1= 1, B0 = 1, B2 = clock sedangkan pin S dan R aktif low, maka flip-flop dalam keadaan toggle. dimana output akan berganti-ganti antara 1 dan 0.

- Apabila B1= 0, B0 = 0, B2 = Don't Care sedangkan pin S dan R aktif low, maka hasil outputnya akan berlogika 1 dan komplemennya juga berlogika 0.

5. Video Percobaan [Kembali]

6. Analisis [Kembali]

1. Apa yang terjadi jika B1 diganti CLK pada kondisi 2?

jawab :

Kondisi 2 pada percobaan 2 ini adalah input B0=1, B1=1, B2= don't care dan B1 diganti dengan clock. Karena B1 dihubungkan ke S dan inputannya berubah-ubah, sedangkan B0 dihubungkan ke R dengan logika 1, dimana pin S dan R adalah aktif low yang aktif apabila berlogika 0. Ketika S berlogika 0 dan R berlogika 1, flip-flop dalam keadaan SET dimana outputnya akan menjadi 1 dan komplemennya 0. Ketika S berlogika 1 dan R berlogika 1, flip-flop dalam keadaan tetap dimana outputnya tetap sperti sebelumnya yaitu 1 dan komplemennya 0.

2. Bandingkan hasil percobaan dengan teori!

jawab :

Berdasarkan teori, ketika S = 0 dan R = 1, maka Q = 1, sama halnya pada percobaan yang telah dilakukan. Tetapi ketika S = 1 dan R = 1, outputnya tetap yaitu Q = 1, sedangkan pada teori ketika S = R = 1, maka outputnya adalah toggle. Hal ini terjadi disebabkan pada percobaan tidak diberikan clock. Jadi S = R =1 jika diberikan clock akan dalam keadaan toggle.

3. Apa fungsi masing-masing kaki Flip-Flop yang digunakan?

jawab :

a. Set (S) = untuk menyetel keluaran flip-flop berlogika 1 bila aktif.

b. Reset (S) = untuk menyetel keluaran flip-flop berlogika 0 bila aktif.

c. Q = menampilkan nilai output dari masukkan.

d. Q' = menampilkan nilai yang berlawanan output.

e. J = nilai input 1

f. K = nilai input 2

g. CLK = dihubungkan ke clock sebagai penentuan kapan output berubah.

7. Download [Kembali]

.jpeg)

Tidak ada komentar:

Posting Komentar