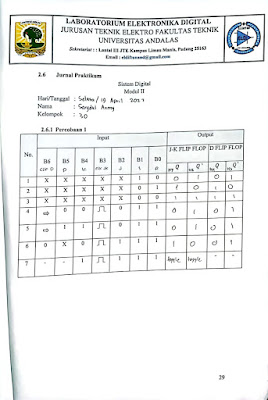

Rangkaian pada percobaan 1 ini menggunakan JK flip flop dengan Set dan Reset, dan D flip flop dengan Set dan Reset. Untuk inputnya adalah switch dengan 7 saklar yang diberi nama B0 – B6 yang dihubungkan dengan VCC untuk logika 1 dan dihubungkan ke ground untuk logika 0. B0 dihubungkan ke R di kedua flip flop, B1 dihubungkan dengan S di kedua flip flop. B2 dihubungkan dengan J pada JK flip flop. B3 dihubungkan pada CLK pada JK flip flop. B4 dihubungkan dengan K pada JK flip flop. B5 dihubungkan dengan D pada D flip flop. B6 dihubungkan dengan CLK pada D flip flop. JK flip flop memiliki 2 output yaitu Q dan Q’, begitu juga dengan D flip flop. Setiap output dihubungkan dengan logic probe sebagai penanda adanya keluaran dari masing masing flip flop.

Pada rangkaian percobaan variasi 1 dengan kondisi B0(R) = 0, B1(S) = 1, B2(J)=don't care, B3(CLK JK)=don't care, B4(K)=don't care, B5(D)=don't care, dan B6(CLK D)=don't care didapat output pada JK flip-flop Q = 0 dan Q' = 1 dan D flip-flop Q = 0 dan Q' = 1. Hal ini disebabkan karena S dan R adalah aktif low, dimana akan hidup apabila berlogika 0. Jadi flip-flop akan dalam keadaan Reset, sehingga ouputnya akan berlogika 0 dan komplemennya berlogika 1 untuk kedua flip-flop.

5. Video Percobaan [Kembali]

6. Analisis [Kembali]

1. Bagaimana jika B0 dan B1 sama sama diberi logika 0, apa yang terjadi pada rangkaian?

jawab :

Jika B0 dan B1 berlogika 0, maka pada output J-K flip-flop dan D flip-flop akan berlogika 1, tetapi komplemen outputnya juga berlogika 1, maka dapat dikatakan bahwa outputnya tidak menentu (undefined) atau dalam kondisi larangan. Hal ini dikarenakan pin S dan R adalah aktif low, dimana akan aktif apabila berlogika 0, sedangkan S dan R berlogika 0, sehingga flip-flop akan dalam keadaan Set dan Reset. Karena itu output dan komplemen outputnya sama yaitu berlogika 1.

2. Bagaimana jika B3 diputuskan/tidak dibubungkan pada rangkaian apa yang terjadi pada rangkaian?

Jawab:

Pemutusan B3 tidak mempengaruhi hasil output dari J-K flip-flop. Output dari J-K flip-flop tetap sebagaimana output sebelumnya. Yang mempengaruhi hasil keluaran dari J-K flip-flop pada rangkaian percobaan adalah S dan R, sehingga perubahan selain dari itu tidak memiliki pengaruh.

3. Jelaskan apa yang dimaksud kondisi toggle, kondisi not change, dan kondisi terlarang pada Flip-Flop!

jawab :

a. Kondisi toggle adalah kondisi dimana outputnya selalu berganti nilai pada setiap pergantian kondisi clock aktif. Misal, jika kondisi sebelumnya beroutput 0, maka selanjutnya akan beroutput 1, 0,1, 0, dan seterusnya.

b. Kondisi not change adalah kondisi ketika nilai keluaran tidak berganti atau tetap.

c. Kondisi terlarang adalah kondisi dimana kedua nilai output Q dan Q' bernilai sama yaitu berlogika 1. Pada RS flip-flop, ketika nilai S = R = 1, output akan menjadi Q = Q' = 1. Hal ini tidak diperbolehkan, karena seharusnya Q' adalah kebalikan dari Q.

7. Download [Kembali]

.png)

Tidak ada komentar:

Posting Komentar